DRAM(Dynamic Random Access Memory)는 무엇인가?

컴퓨터는 폰 노이만 구조(von Neumann Architecture)에 따라서 Central Processing Unit인 CPU 그리고 메모리 장치가 분리된 구조를 가지고 있습니다. 그렇기 때문에 CPU는 저장장치인 메모리디바이스에서 원하는 데이터를 읽고, 쓰고, 지우는 작업을 수행하죠. 컴퓨터가 꺼져도 사라지지 않는 그런 메모리들은 비활성(non-volatile) 메모리인 NAND Flash에 저장을 하고 있습니다. 컴퓨터에 끼워져 있는 SSD가 NAND Flash이죠. 그런 NAND Flash는 특성상 매우 큰 데이터를 저장할 수 있지만 상대적으로 CPU가 원하는 데이터를 바로 제공해주기에는 느린 속도를 가지고 있습니다. 아무리 많은 데이터를 갖고 있더라도 데이터를 주고 받는 통로가 좁으면 의미가 없는 것이죠. 결국 Bottleneck(병목) 현상이 발생하여 Computing 속도를 매우 낮추게 됩니다. 그런 문제점을 해결해주는 역할을 수행하는 것이 DRAM이라는 장치입니다. CPU가 원하는 데이터를 매우 빠른 속도로 제공해주기 때문에 DRAM은 컴퓨팅 성능에 매우 중요한 역할을 수행하고 있습니다.

DRAM의 1T1C구조는 무엇인가?

DRAM은 1T1C의 구조라고 불리죠. 하나의 Transistro그리고 하나의 Capacitor로 이루어져 있습니다. 위와 같이 Symbol로 나타낼 수 있죠. DRAM이 데이터를 저장하는 방식은 Capacitor에 저장된 charge에 의해서 이루어집니다. Capacitor의 charge state에 따라서 1과 0을 구분하고 데이터를 저장할 수 있는 것이죠. Capacitor에 전하가 저장되어 데이터를 저장하기 때문에, Storage Capacitor라고 부르기도 합니다.

위의 그림에서 Select라고 적혀 있는 line은 WL(Word-Line)이라고 부릅니다. WL(Word Line)이 Transistor(Tr)의 On/Off를 결정하는 metal line인 것이죠. MOSFET의 Gate에 연결되어있는 배선이라고 생각하시면 됩니다. Data라고 적혀있는 line은 BL(Bit Line)이라고 부릅니다. Read와 Write 동작을 수행하기 위해 전압을 인가하는 metal line입니다. 마지막으로 Storage Capacitor라고 적혀있는 Symbol은 당연히 전하를 저장하는 축전기를 나타냅니다.

실제로 소자를 반 잘라서 TEM이미지를 보면 위와 같이 생겼습니다. WL이 Tr의 gate라고 보시면 되고 MOSFET에서 익히 등장하는 Source와 Drain이 존재합니다 그리고 Source에서 Contact이 되어 위의 Capacitor로 연결이 되어 있죠. Plate Poly는 Cap을 구성하는 metal로 일정한 전압(Vcc/2)가 인가되어서 Cap의 열화를 방지하는 역할을 수행합니다.

DRAM은 어떤 방식으로 동작하는가? Read 그리고 Write ?

DRAM의 Read/Write 동작을 위해서는 각각의 metal line에 특정한 전압이 인가되어야 합니다.

*Write=Program

일반적으로 DRAM의 동작은 물이 차오르고 빠지는 수조와 비교를 많이 합니다. 그래서 그 비유를 사용해보도록 하겠습니다.

수조 = Capacitor

수문 = WL(Transistor On/Off 결정)

물 높이 = Capacitor Voltage

수조 사이즈 = Capacitance(정전용량)

(Capacitance가 클수록, 전하를 더 많이 저장하기 때문에 수조의 사이즈가 크다고 볼 수 있다)

(저장되어 있는 전하의 양이 많을 수록 상대적인 0과 1의 차이를 파악하기 쉽다=큰Cc)

<Write 동작 수행 방식>

write는 Capacitor에 전하를 저장하는(=데이터를 저장) 동작이다.

"1" 저장하기

WL = Vpp

Cap에 전하를 저장하기 위해서는 먼저, WL에 Vpp(~3V)를 인가하여 Tr.을 On시킨다

BL=Vcore

Tr가 켜져 Channel이 형성되어 전류가 흐르는 상태에서 BL전압을 인가한다

Tr에 흐르는 전류를 통해 결과적으로 Cap이 충전되어 데이터 1이 저장된다

"0"저장하기

WL=Vpp

동일하게 Tr을 On시킨다

BL=Vss(~0V)

Bit Line에 0V를 인가함으로 Cap에 0을 저장한다.

(0V라고 전류가 흐르지 않는 것이 아님)

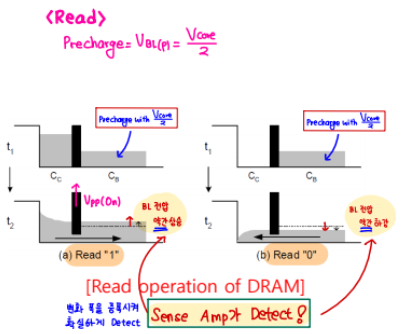

<Read동작 수행 방식>

read는 Capacitor에 저장되어있는 데이터를 읽는 과정입니다.

DRAM은 Capacitor에 저장된 전하의 양을 상대적으로 비교하면서 데이터를 읽게 됩니다. 그리고 그 과정에서 Charge Sharing 개념 이 사용됩니다.

가장 처음에 BL에 precharged된 전압인 Vcc/2가 인가됩니다.

Vcc/2는 Low인 0V와 High인 Vcc인 중간 값이기 때문에, Capacitor에 저장되어 있는 전하의 양을 판별하는 중간 기준치가 되어줍니다.

"1"이 저장되어 있던 경우

BL=Vcc/2가 precharged

WL=Vpp(Tr On)

결과 : Cap에 전하가 저장되어 있었기 때문에, BL의 전압이 소폭 상승함 = △Vh

"0"이 저장되어 있던 경우

BL=Vcc/2가 precharged

WL=Vpp(Tr On)

결과 : Cap에 전하가 저장되어 있었기 때문에, BL의 전압이 소폭 하강함 = △Vl

결론적으로 저장되어있는 상황과 상관없이, DRAM의 WL과 BL동작은 동일합니다.

중요한 것은 WL과 BL전압 인가 이후에 발생하는 전압 변화의 차이입니다.

아래 수식으로 전압 변화가 발생하는 원인에 대해 알아봅시다.

좌측 D1케이스는 Charge가 저장되어있던 "1"상황

우측 D0케이스는 Charge가 저장되어 있지 않던 "0"상황입니다

결과적으로 전하량 보존의 법칙에 따라서 Charge의 양이 변하는 것을 Detecting하여 데이터를 읽을 수 있는 것이죠.

DRAM이 발전하는 방향은 그래서 무엇인가?

위 DRAM의 동작 원리를 바탕으로 보더라도 결국 DRAM의 우수한 동작을 위해서는 Capacitor가 전하를 저장할 수 있는 용량인 정전 용량(Capacitance)를 키우는 것이 중요합니다. 모든 소자는 완벽히 제어되고 설계되었다고 하더라도 예상치 못한 electron의 이동이 발생 할 수 있습니다. DRAM의 경우에는 그런 electron의 이동은 charge loss와 관련이 있죠. 저장되어있던 data가 변형되는 것을 의미합니다.

처음에 사용자가 data를 저장하여 capacitor에 "1"이 저장되었다고 합시다. charge들이 잔뜩 저장이 되어있다는 의미겠죠. 하지만, 만약에 의도치 않은 leakage current가 발생하여 charge들이 일부 소실되었다면 어떻게 될까요? 정전용량(Capacitance)가 커서 굉장히 많은 전하들이 저장이 되어있었다면 charge loss가 일부 발생하더라도 큰 차이가 없겠죠. 하지만, 반도체는 Scaling Down이 되며 집적화되고 있습니다. DRAM의 사이즈도 매우 작아지면서 Capacitor의 크기도 굉장히 작아지고 있죠. Capacitance가 작아질 수 밖에 없는 것이죠. 그런 상황에서 leakage current로 인한 charge loss는 데이터의 왜곡을 야기시킬 수 있습니다. 저장된 메모리가 변형되면 굉장히 큰 issue죠. 따라서 DRAM은 사이즈가 작아지는 Scaling Down의 흐름속에서도 Capacitance를 키울 수 있는 방향으로 연구가 이루어지고 있습니다.

Capacitance는 위와 같은 수식으로 나타낼 수 있습니다.

A는 평판의 면적인데 이를 키우면 오히려 소자의 사이즈가 커지니까 Scaling Down을 거스르는 흐름이죠.

t는 평판사이의 거리입니다. 가깝게 하면 좋겠지만, 일정 두께 이하가 되어 버리면 Tuennling이 발생할 수도 있고 leakage가 굉장히 커지게 됩니다. 그렇기 때문에 이를 줄이는데도 한계가 있죠.

따라서 마지막으로 남은 parameter가 ε(유전상수) 입니다.

이 유전상수가 큰 유전체(dielectric)을 연구하여 Capacitance를 키우는 것이 현재의 흐름입니다. 지금까지 어떤 유전체가 사용이 되었고 현재 어떤 유전체와 전극을 사용한 연구가 진행되고 있는지는 다른 글에서 이어서 설명을 하겠습니다.

DRAM Capacitor의 Capacitance를 늘리기 위한 발전 방향

DRAM의 발전 방향은 위의 논문을 일부 참고하여 글을 작성하였습니다. DRAM의 발전은 어떻게 이루어지고 있는가?DRAM은 위와 같이 끊임 없이 미세화가 되고 있습니다. 그에 따라서 Capacitance는 효율

wanstradamus.tistory.com

'반도체 공부' 카테고리의 다른 글

| [DRAM Capacitor] 종류와 동작원리 그리고 SDRAM,SDR, DDR (0) | 2024.06.06 |

|---|---|

| [DRAM Capacitor의 발전] DRAM구조와 동작원리, High-k (0) | 2024.05.31 |

| [반도체 물성, 물리전자] 쇼트키(Schottky) 접합, 옴(Ohmic) 접합 (0) | 2024.05.30 |

| [전기전자] Impedance 임피던스는 무엇인가? (0) | 2024.05.22 |

| [반도체 물성, 물리전자] 페르미 레벨(Fermi Level) N-type, P-type반도체 (0) | 2024.05.16 |