DRAM은 현재 반도체 시장에서 Logic 반도체와 더불어 가장 중요한 메모리 반도체의 한 종류이다.메모리 반도체를 보통 휘발성인 Volatile과 비휘발성인 non-Volatile 메모리로 구분되고 DRAM은 휘발성 메모리의 일종이다.

그럼 메모리 소자의 중심에 있는 DRAM에 대해서 한 번 자세히 정리 해보자.

DRAM의 구조

DRAM의 구조는 가장 간단하다.

1Transistor 1Capacitor

흔히 그냥, 1T 1C 라고 한다. (SRAM은 6T구조)

위 사진에서 보이는 것 처럼, Transistor가 하나 존재하고 전하를 저장하는 Capacitor가 존재한다. Capacitor에는 전하가 저장되고 방출되면서 데이터 1과 0의 1bit를 나타낼 수 있게 된다.

Capacitor에 전하가 저장되어 데이터를 저장하기 때문에, Storage Capacitor라고 부르기도 한다.

WL(Word Line) : Tr의 ON/OFF를 결정하는 metal line

BL(Bit Line) : Read와 Write 동작을 수행하기 위해 전압을 인가하는 metal line

Plate Poly : Cap을 구성하는 metal로 일정 전압(Vcc/2)가 인가되어 Cap의 열화를 방지한다.

실제 위와 같이 DRAM이 구성이 된다.

DRAM Cell 동작

DRAM의 Read/Write 동작을 위해서는 각각의 metal line에 특정한 전압이 인가되어야 한다.

* Write=Program

DRAM 동작을 이해하는 과정에서 DRAM을 보통 수조와 비교한다.

수조 = Capacitor

수문 = WL(Transistor on/off 형성 여부)

물 높이 = Capacitor Voltage

수조 사이즈 = Capacitance

(Capacitance가 클 수록, 전하를 많이 저장하기 때문에 수조의 사이즈가 크다고 볼 수 있다)

-> 저장되어 있는 전하의 양이 많을 수록 상대적인 차이를 파악하기 쉽다.(= 큰 Cc)

* Cc = 20~30 fF CB = 200~300fF

* Bit Line은 Cell Array에서 물리적으로 Cell Cap에 비해 큰 metal이다. 따라서 CB값이 더 크다.

( CB는 기생 의도치 않은 Capacitor이기 때문에 작을 수록 좋다)

1. Write 동작

write는 Capacitor에 전하를 저장하는 즉, 데이터를 저장하는 operation이다.

<1 저장하기>

1) WL = Vpp

Cap에 전하를 저장하기 위해서는 먼저, WL에 Vpp(~3V)를 인가하여 Tr.를 ON시킨다.

2) BL = Vcore

Tr.가 켜져 Channel이 형성되어 전류가 흐르는 상태에서 BL전압을 인가한다.

Tr에 흐르는 전류를 통해 결과적으로 Cap이 충전되어 데이터 1이 저장된다.

<0 저장하기>

1) WL = Vpp

동일하게 Tr을 ON 시킨다.

2) BL = Vss(~0V)

Bit Line에 0V를 인가함으로 Cap에 0을 저장한다.

(0V라고 전류가 흐르지 않는 것이 아님)

* D1 : "1" 이 저장된 상황

* D2 : "0" 이 저장된 상황

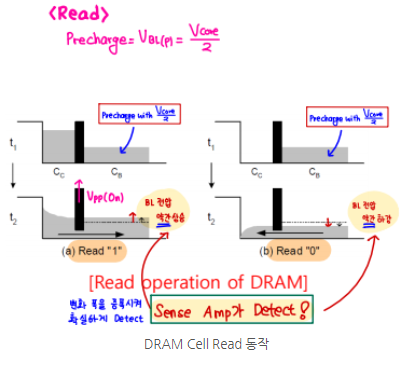

2. Read 동작

read는 Capacitor에 저장되어있는 데이터를 읽는 과정이다.

DRAM은 Capacitor에 저장된 전하를 양을 상대적으로 확인하는 과정을 통해서 데이터를 읽게 된다.

그리고 그 과정에서 Charge Sharing이 사용된다.

가장 처음으로 BL에 precharged된 전압인 Vcc/2가 인가 된다.

Vcc/2는 LOW인 0V와 High인 Vcc 의 중간 값이기 때문에,Vcc/2는 Capacitor에 저장되어있는 전하로 인한 Voltage 변화량을 측정하는 중간값, 기준치가 되어준다.

< D1("1" 저장 상황) >

1 ) BL = Vcc/2 가 precharged

2) WL = Vpp (Tr. ON)

결과 : Cap에 전하가 저장되어 있었기 때문에, BL의 전압이 소폭 상승함 = ΔVH

< D0("0" 저장 상황) >

1 ) BL = Vcc/2 가 precharged

2) WL = Vpp (Tr. ON)

결과 : Cap에 전하가 저장되어 있지 않았기 때문에, BL의 전압이 소폭 하강함 = ΔVL

결론적으로 저장되어있는 상황과 상관없이, DRAM의 WL과 BL동작은 동일하다.

결국 중요한것은, WL과 BL 전압인가 이후에 발생하는 전압 변화의 차이이다.

아래 수식으로 전압 변화가 발생하는 원인에 대해 알아보자.

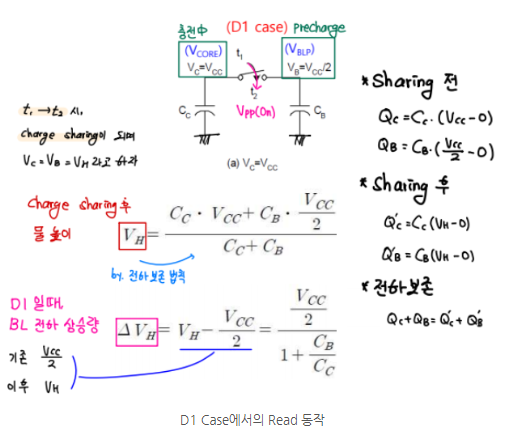

< D1 Case >

위처럼 WL에 Vpp 전압이 인가되기 전과 후에도 전하량이 같다는 "전하량 보존 법칙"을 사용한다. 결과적으로 Cap에 저장되어있는 전하로 인해 변화된 BL의 전압 변화량은 위와 같다.

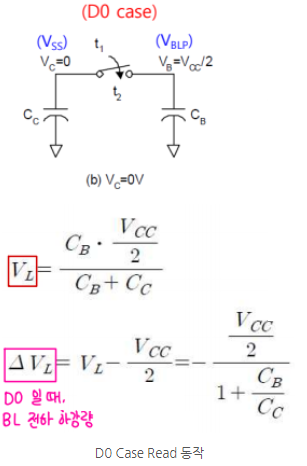

같은 방식으로 D0 Case도 정리하여 아래와 같이 수식으로 나타낼 수 있다.

< D0 Case >

이전에 Cc는 수조의 높이 즉, 전하가 저장되는 양을 나타내는 값이기 때문에, 클 수록 좋고

BL의 Capacitance값을 나타내는 CB는 기생 값이기 때문에 작을 수록 좋다고 했다.

그 이유는 위의 ΔVH ΔVL 의 수식에서 나타나진다.

CB가 작고 Cc가 커야 전압 변화량이 커 Detection이 쉬워진다

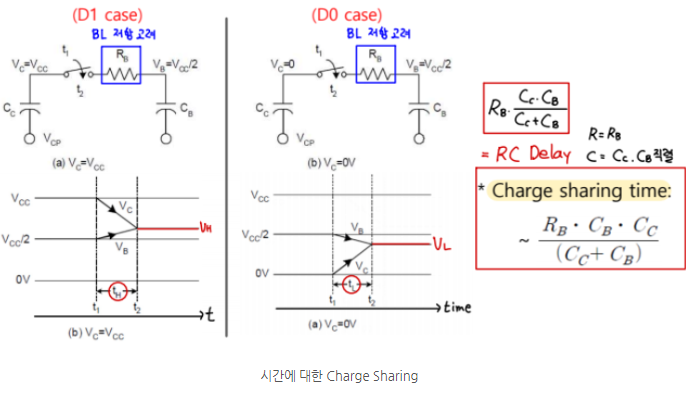

추가적으로 BL metal line에 존재하는 저항 성분을 줄이는 것도 매우 중요하다.

그 이유는 RC Delay time과 관련이 있다.

Charge Sharing이 아주 짧은 한 순간에 발생하는 것이 아니기 때문에, 전압이 변화하는 delay time이 존재하고 이는 회로의 동작 Speed에 아주 중대한 영향을 미친다.

당연히 RC Delay값이 작을수록 DRAM의 Read operation 동작 속도가 빨라진다.

Charge Sharing time 수식을 통해 결론적으로 BL metal Line의 기생 저항을 줄이는 것이 중요함을 알 수 있다.

*BL의 기생저항은, 채널저항 컨택저항 등... 으로 구성된다.