Retention of DRAM ; DRAM의 전하 보존 능력

DRAM의 발전 방향을 이해 하기 위해서는 DRAM의 동작 원리를 이해해야한다. 구조와 동작 원리는 아래 글에서 다루었다.

DRAM의 구조와 동작 원리, 장단점. DRAM은 무엇일까?

DRAM은 현재 반도체 시장에서 Logic 반도체와 더불어 가장 중요한 메모리 반도체의 한 종류이다.메모리 반도체를 보통 휘발성인 Volatile과 비휘발성인 non-Volatile 메모리로 구분되고 DRAM은 휘발성 메

wanstradamus.tistory.com

DRAM에 있어서 본질적인 목적은 결국 Data Retention(데이터 보존 능력) 이다. 메모리 소자가 가져야 할 필수적인 능력이기에 당연히 NAND에도 적용이 되는 말이다. 아무리 빠른 속도로 Data를 Write(=Program)하더라도 저장된 charge에 빠르게 소실 된다면 데이터로 아무런 의미가 없을 것이다. 그렇기 때문에 charge를 저장하는 능력 즉, Retention ability는 DRAM의 매우 중요한 요소이다.

결국, DRAM에서 가장 중요한 역할을 하는 부분은 전하를 저장하는 Capacitor이다. 1T 1C 구조를 가지는 DRAM은 Tr.에서 발생하는 Junction Leakage와 더불어 Capacitor가 가지는 Defect로 인한 누설 전류 뿐만 아니라 Cell Array에서 발생하는 모든 누설 전류를 최소화 시켜야 한다.

대표적으로 Data Retention을 저해하는 요소는 아래와 같다.

1. Junction Leakage

PN Junction의 Reverse bias가 인가 되었을 때, Minoirty carrier로 인한 전류가 작지만 흐를 수 있다. 추가적으로 doping에 따라 Band Bending이 발생하고 높은 전압이 인가된다면 Tunneling으로 인한 BTBT로 전류도 흐를 수 있다.

2. GIDL

VGD < 0 으로 Drain의 전압이 Gate보다 큰 상황에서 Gate-Drain의 Overlap된 계면에서 큰 Band Bending으로 인해 누설 전류가 발생하는 현상이다

3. Channel Leakage(Ioff)

Vth(임계전압) 이하의 Subthreshold영역에서 흐르는 전류로 Gate에 전압을 인가하여 Tr.을 작동시키지 않았을 때 흐르는 전류로 소자가 동작하지 않는 대기 상태에서 발생하는 누설전류이다.

4. Isolation Leakage

일반적으로 Cell과 Cell 사이에 전류가 흐르지 않고 절연체로 완벽히 구분되어 있지만 절연층의 Defect에 의해서 의도치 않은 누설 전류가 발생 할 수 있다. 이는 저장된 Charge를 소실하는 것 이외에도 인접한 neighbor Cell의 Data Distortion을 발생시킬 수 있다.

5. Capacitor Leakage

Capacitor의 절연층에 Trap과 같은 Defect이 존재 할 수 있고 이로 인해 누설 전류가 발생 할 수 있다.

위의 요소들 이외에도 MOSFET에서 다루었던 여러 SCEs로 인한 누설 전류와 Gate Oxide의 Defect이 가지는 누설 전류 그리고 Scaling Down으로 인한 Oxide Tunneling과 같은 모든 요소들이 DRAM의 Retention에 영향을 준다.

Retention Time

위처럼 누설전류로 인해 Retention Time이 존재하고, DRAM의 경우에 누설 되는 Charge를 극복하기 위해 Refresh를 한다. Refresh 동작은 DRAM에서 가장 중요한 동작이고 Refresh를 하기 때문에 Dynamic RAM이라고 부른다.

당연히 Refresh Cycle이 많아 질 수록, 추가적인 전력이 들어가는 것이기 때문에 Retention time을 최대한 늘리고 Refresh 횟수를 줄이는 것이 중요하다.

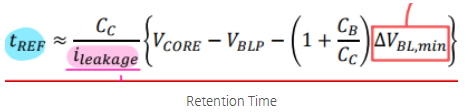

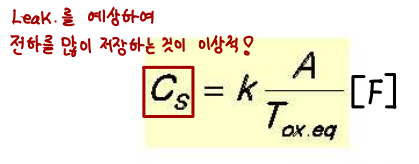

그럼 수식으로 Retention Time을 유도 해보자.

결과적으로 위와 같은 식으로 유도 될 수 있는데,

ILeakage는 누설 전류를

ΔVBL,min은 감지 할 수 있는 최소 전압 변화량을 의미한다.

위의 유도를 살펴보면, 원래는 Cell Capacitor가 누설전류 없이 Vcore에서 Sharing 후 VH로 변화된다. 결과적으로는 Vcore -> VH 로 변화되고 ΔVH = VH - VBLP 로 나타낼 수 있다.

하지만, 누설전류가 존재하여 전압 변화량을 감지하는 임계값 까지 떨어졌다고 가정을 해보자. Vcore' -> VH' 따라서, ΔVH' = VH' - VBLP = ΔVBL.min으로 나타낼 수 있다.

그 이후, 이전의 전하량 보존 법칙을 사용하여 Vcore'에 대한 수식을 얻을 수 있고 이를 통해 ΔQ를 유도, 결과적으로는 시간인 t에 대한 식을 나타낼 수있고 이 값이 바로 Retention Time이다.

수식에서도 알 수 있지만, Cell Capacitor값인 Cc가 클수록, 저장된 Charge가 소실된는 Leakage 전류값이 작을수록 Retention Time이 늘어난다😀

Evolution of DRAM; DRAM의 발전 방향

결과적으로 DRAM 소자의 신뢰성(Reliability)를 높이면서 동시에 집적도를 높이기 위해 여러 방향으로 연구가 진행되었다.

SCEs(Short Channel Effects)로 인한 Gate Controllability 저하 혹은 누설전류를 제어하는 것이 필요하다. 단순하게 기존의 DRAM의 MOSFET은 집적화에 따라 Length가 이미 일정 수준 이상으로 짧아 졌기 때문에 물리적으로 Leff를 늘린 방법을 적용한 소자가 RCAT이다.

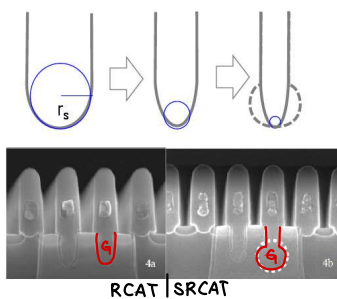

< RCAT > Recess Chanel Array Transistor(100nm ~ 70nm tech.)

RCAT의 구조를 보면 기존의 Planar와 달리 Gate가 포물선의 형태로 아래로 깊게 파여있다. Gate를 아래로 깊에 파는 Recessed 형태로 Channel의 길이가 물리적으로 늘어나게 되었다. 결과적으로 SCEs를 완화 시킬 수 있는 구조인 것이다.

Recessed 구조의 장점 (Curvature Effect)

Leff 증가😀

Vth 증가 😀 : Gate 아래 Inversion Layer를 형성해야 하는 물리적인 길이가 증가 했기 때문에 Vth가 증가한다.

-> Junction Leakge 감소

Cox 감소😭 : Gate가 Control 해야하는 영역이 증가 했기 때문에, Gate의 제어력을 나타내는 Cox가 감소한다.

따라서 RACT은 기존의 Planar 구조에 비해 Leakage를 감소시켜 Retention time이 늘어난다.

<S- RCAT > Sphere-Shaped Recess Chanel Array Transistor(70nm ~ 50nm tech.)

S-RCAT은 RCAT보다 진보된 형태의 구조이다.

위의 그림 처럼 Gate 끝을 둥글게 만들어 Channel의 물리적인 길이도 증가시키고 Gate 제어력도 증가시킨다.

RCAT의 단점 중 하나는 Cox가 감소된다는 점인데 Gate 끝을 뭉퉁하게 증착하여 Cox를 오히려 증가시킬 수 있다.

Sphere-Sahped 구조의 장점

Cox 증가😀

Leff 증가😀

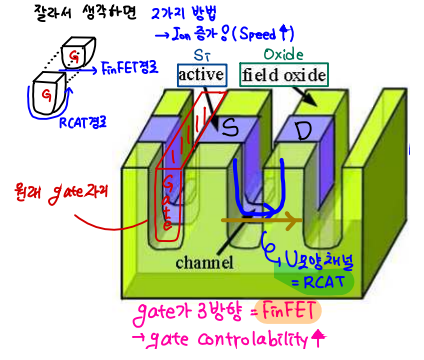

<S- Fin Tr. > Saddle Fin Transistor(50nm ~ 20nm tech.)

S-Fin 구조는 위처럼 Gate의 형태를 입체적으로 구성하여 FinFET처럼 Channel을 3방향으로 감싸는 효과와 기존의 RCAT 효과를 동시에 가져 갈 수 있다.

*Saddle : (말에 앉는) 안장

현재 DRAM에 사용되는 구조로 Gate의 Controllability를 극대화 시켜 Cox를 증가시킴과 도시에 물리적인 Channel길이도 크게 가져갈 수 있기 때문에 누설전류를 매우 효과적으로 관리 할 수 있다.

당연히 Data Retention이 기존에 소개 했던 RCAT이나 S-RCAT에 비해 매우 길다.

Saddle Fin Tr. 구조의 장점

Cox 매우 증가😀

Leff 증가😀

Ion 증가😀

* 기존에 RCAT과 S-RACT 구조에서 물리적인 Leff를 길게 가져갔기 때문에, Ion이 감소되는 단점도 존재했다.

Ion의 Current 식이 W/L 과 비례하기 때문에 Saddle Fin 구조는 이런 단점도 극복한 구조라고 볼 수 있다.

*Ion은 Tr의 동작 Speed와 관련이 있기 때문에 Ion을 높일 수록 Tr.의 동작 속도가 빨라진다.

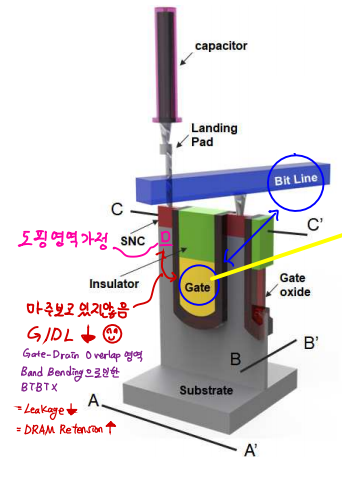

<BCAT > Buried Cell Array Transistor(20nm ~ )

위 처럼 Gate가 S/D 보다 아래에 존재하는 Buried 구조는 보다 효과적으로 누설 전류를 차단한다.

Buried Cell Array Tr. 구조의 장점

GIDL 방지😀

: GIDL은 gate와 drain이 overlap 되는 계면에서 발생하는 band bending이 원인이었기 때문에, buried된 gate를 통해 G-D overlap 영역을 만들지 않아 GIDL이 방지된다.

기생 Cap 감소😀

기존에 Gate와 연결된 WL metal과 BL metal이 인접했기 때문에 기생 Cap이 발생했었다. 하지만, BCAT의 경우에는 Gate가 buried되어 BL과의 물리적인 길이가 멀어졌기 때문에, BL Cap이 감소한다.

Capacitor 발전 방향

누설전류를 차단하여 Retention 능력을 높이는 것

Capacitor가 최대한 많은 양의 전하를 저장하는 것

결국 Capacitor의 발전 방향은 위와 같다.

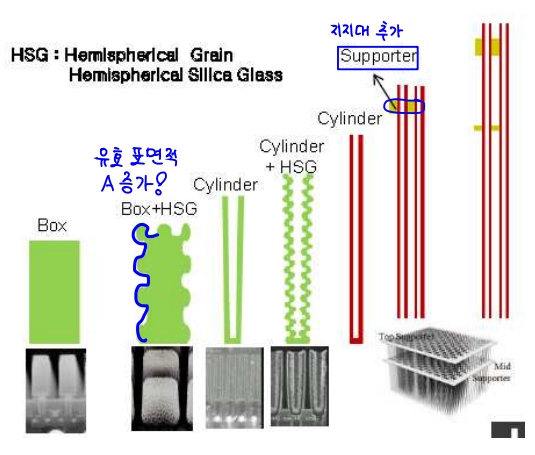

Capacitor의 저장능력 Capacitance를 늘리기 위해서는 위 수식에서도 알 수 있지만, 단면적(A)를 넓히거나 M-I-M구조에서 Insulator의 두께를 최소하하는 것이 필요하다. 그런 방향이 아래처럼 나타난다.

처음의 BOX형태의 Capacitor에서 보다 많은 단면적을 가져가기 위해 HSG구조를 채택하여 같은 부피에 보다 많은 유효 면적을 가지는 Cap을 만들 수 있었다. 추가적으로 Cylinder구조를 아주 얇고 높게 적층하면서 보다 큰 Cap값을 가지게 되었다.

하지만, 반도체의 사이즈를 줄이는 Scaling Down의 흐름에서 단면적을 넓히는 것은 그에 반대되는 행동이다. 따라서 더이상 구조적으로 어려움에 봉착했다. 절연체의 두께를 줄이는 것은 이상적이지만 두께가 얇아짐에 따라서 Direct Tunneling이 발생할 수 있고 절연체가 여러 Defect에 매우 취약하게 된다. 결국 높은 유전상수(ε)를 가지는 절연체를 찾는 것이 중요하다.

현재는 SiO2가 아니라 ZrO2, HfO2, TiO2, ZAZ(ZrO2/Al2O3/ZrO2)와 같은 절연체들이 사용중이고 연구중이다. 그리고 더 나아가서는 3성분계물질인 STO(SrTiO3) 들이 활발히 연구중에 있다. 결국 유전율과 bandgap이 가지는 Trade-off관계속에서 유전율도 높으면서 bandgap이 높아 leakage current를 줄일 수 있는 물질을 증착하는 것이 매우 중요한 흐름이다.

ALD 장비를 활용하면서 우수한 Dielectric 그리고 그에 맞는 Electrode를 사용하는 것이 관건이다.