이번에는 DRAM(Dynamic Random Access Memory) 소자의 최근 발전에 대해서 이야기 해보고자 합니다.

사실 DRAM이라기보다 좀 더 넓혀서 Transistor의 발전 방향이라고 해도 무방할 것 같네요.

DRAM Capacitor의 발전 방향

1975년에 Trench Capacitor DRAM이 처음 특허로 출헌 되었을 때가 위 사진의 모습입니다. 우측의 SEM 이미지를 보시면 아시겠지만, 저희가 익히 알고 있는 1T 1C의 구조를 가지고 있죠. Gate가 존재하고 옆에 Trench 구조로 파여져 Capacitor를 구성하고 있습니다.

현재는 조금 더 발전한 구조로 DRAM의 구조가 이루어져 있죠.

같은 면적에서 더 많은 Capacitor 용량을 구현하기 위한 발전.

그리고 Scaling Down을 통해서 최소한의 면적에서 Transistor와 Capacitor를 구현하는 노력이 이루어지고 있습니다.

위는 Pillar Type의 Capacitor 구조입니다. 같은 Pillar Type 임에도 Capacitance가 높아질 수 있는 이유는 Area(면적)을 넓히기 위해 같은 Pillar더라도 구조적으로 더 좁고 높은 Pillar를 쌓아 올렸기 때문이죠. 구조적으로 큰 Capacitance를 갖기 위한 연구 방향 이외에도 더 높은 유전 상수를 가지는 High-k 물질을 사용하여 상대 유전율을 높이는 방안도 연구가 활발히 이루어지고 있죠. 그렇게 현재 DRAM에서 사용 중인 물질은 ZAZ(ZrO2/Al2O3/ZrO2)입니다. 그리고 전극으로는 TiN의 전극을 사용하고 있죠.

(혹시 ZAZ Capacitor에 관심이 있으시다면, 추후에 올릴 글을 참고해주세요)

Capacitor 구조의 발전 방향과 관련에서는 아래 글에 정리해 두었으니 참고하시면 될 것 같습니다.

[DRAM Capacitor] 구조와 발전방향, RCAT, S-RCAT, S-Fin Tr, BCAT, DRAM Capacitor

Retention of DRAM ; DRAM의 전하 보존 능력DRAM의 발전 방향을 이해 하기 위해서는 DRAM의 동작 원리를 이해해야한다. 구조와 동작 원리는 아래 글에서 다루었다. DRAM의 구조와 동작 원리, 장단점. DRAM

wanstradamus.tistory.com

DRAM Capacitor의 문제점들...

하지만, 더 나아간 미래에는 DRAM이 Capacitor를 가지기 때문에 발생하는 문제를 해결하기 어려워지는 순간이 올거라고 다들 생각하고 있습니다. 이미 어느정도 한계점에 봉착하고 있죠. 구조적으로는 3D Stacking을 하지 않는 한 더 높은 면적을 확보하여 정전 용량을 높이는 방향은 이미 임계점에 도달하였고, ZAZ 유전체보다 더 높은 Dielectric을 사용하는 것을 활발히 연구 중에 있지만 아직까지는 산업화 하여 사용 할 수 있는 유전체를 활용하기에는 긴 시간이 남았죠. 그래도 가장 가능성이 높은 것은 TiO2를 유전체로 활용하는 것이 아닐까 싶습니다만, TiO2가 가지고 있는 Leakage 문제 그리고 TiO2의 Phase를 조절하여 rutile-phase의 TiO2를 만들어야하는 것이 큰 도전 과제이죠.

지금 당장 사용하고 있는 문제점은 아래와 같다고 볼 수 있습니다.

Capacitor가 차지하는 큰 면적

DRAM은 CPU와 조금은 떨어진 위치에 탑재 되어 주기억장치의 역할을 수행합니다. 그리고 해당 1T 1C의 DRAM은 상대적으로 Transistor에 비해 매우 큰 면적을 차지하는 Capacitor의 존재로 인해서 면적의 손실이 이만저만이 아니죠.

위 사진은 DRAM Capacitor의 단면도를 나타내는 TEM 사진입니다. 한눈에 보더라도 Capacitor가 하단의 Transistor와 비교하였을 때 얼마나 큰 면적을 잡아먹고 있는지 알 수 있죠. 공정에 있어서 Aspect Ratio는 가로 길이 대비 세로길이를 나타내는 Parameter입니다. 이 것이 클 수록 좁은 면적에 높이 물질을 쌓아 올려야 하는 것을 의미하는데 현재 Samsung, Hynix와 같은 회사의 Capacitor Aspect Ratio는 약 25에 해당됩니다. 가로 대비 세로의 길이가 1:25에 해당되는 것이죠. 이런 문제는 아래 공정의 문제와도 연결이 됩니다.

Capacitor 공정의 어려움

결국 앞서서 설명을 드렸지만, Capacitance를 최대화 하기 위해서 최대한의 면적을 확보하기 위해 Trench 구조를 넘어서 굉장히 복잡하고 어려운 구조의 DRAM을 활용하고 있습니다. Pillar Type으로 단순히 기둥으로 쌓아 올린 것을 넘어서 HSG 형태로 꼬불 꼬불한 면을 만드는가 하면 Cylindrical하게 원기둥으로 쌓아 올리기도 하죠. 뿐만 아니라 앞서서 설명을 드렸듯이 가로 대비 세로의 비율이 Aspect Ratio는 점점더 커져만 가고 있습니다. 결국 수많은 공정 Step을 통해서 제작을 해야 하고 그런 공정 Step 하나하나가 발생시키는 Budget은 산업적인 측면에서 굉장히 크게 다가올 수 밖에 없습니다. 가격적인 측면, 생산 시간적인 측면에서요.

위에서 언급되어 있는 것은 DRAM에 EUV 장비를 적용한다는 이야기입니다. EUV에서는 다들 잘 아실거라고 생각합니다. 굉장히 극단파장을 사용하여 Lithography를 하여 최소 선폭을 가져가겠다는 이야기죠. 아직도 DRAM이 잘 발전되어가고 있구나 하고 생각하기 보다는 EUV를 이제 사용해야지만 DRAM이 발전 할 수 있는 한계치에 도달하고 있다는 것이죠. 공정적으로 더욱 더 어려워지고 있다는 반증이기도 합니다.

Capacitor의 Refresh 동작으로 인해 발생하는 전력 손실

DRAM은 전하를 Capacitor에 저장하겨 Write 동작을 수행하고. 해당 데이터를 읽기 위해서는 전하를 빼내어 S/A가 미세한 Voltage 변화를 감지하여 저장 된 데이터를 읽어 냅니다. 결국 DRAM은 데이터를 읽기 위해서는 저장되어있는 전하를 빼어내기 때문에 읽고 나서 다시 전하를 채우는 과정이 필요하고 이 과정을 Refresh 과정이라고 칭합니다. 이렇듯 주기적으로 refresh를 해줘야 하기 때문에 DRAM의 이름이 Dynamic RAM이기도 한 것이죠. 다시 본론으로 돌아와서 이렇듯 Refresh를 주기적으로 해줘야하는 DRAM의 동작 특성 상 전력 소모가 발생하게 됩니다. 장비를 유지하는데 있어서 계속해서 전력을 소모해야하는 것은 그렇지 않은 소자에 비해서 너무나 큰 단점이죠.DRAM의 Refresh 동작 및 기타 동작에 대해서는 아래 정리 되어 있습니다. 참고해주세요.

[DRAM Capacitor] 구조와 동작 원리, 장단점. DRAM은 무엇일까?

DRAM은 현재 반도체 시장에서 Logic 반도체와 더불어 가장 중요한 메모리 반도체의 한 종류이다.메모리 반도체를 보통 휘발성인 Volatile과 비휘발성인 non-Volatile 메모리로 구분되고 DRAM은 휘발성 메

wanstradamus.tistory.com

SRAM의 역할과 단점

지금은 잠깐 DRAM이 아니라 SRAM에 대해서도 잠깐 언급을 하고자 합니다.

6개의 Transistor로 이루어져 Flip flop의 동작으로 Cashe memory를 저장하는 SRAM 은 Capacitor는 없지만, 6개의 Transistor로 구성되어 있는 구조입니다. 속도가 DRAM에 비해서는 굉장히 빠르기 때문에 캐시용으로 사용되지만 대신 전력 소모가 크죠(Transistor가 6개니까) 그리고 당연히 6개의 Transistor로 구성되어있다는 것 자체도 면적을 차지하게 됩니다. 물론, Capacitor에 비해서는 미미하겠지만요.

속도가 빠르기 때문에 캐시 메모리로 활용되는 SRAM. 하지만, 적은 용량과 높은 제조 비용.

그렇다고 해서 DRAM을 CPU에 붙여 활용을 하기에는 공정 프로세스가 다르기 때문에 BEOL(Back End of Line)에서 적용할 수가 없고, 발열 관리에 어려움이 있죠.

만약 SRAM의 용량을 조금 더 늘리면서, 동시에 속도는 DRAM보다 빠르고 Capacitor가 없어 최소한의 면적만 사용 할 수 있다면 어떨까요? Capacitor 없이 전하를 저장할 수 있는 소자를 만들면 됩니다.

2T 0C : Capacitorless 소자의 등장

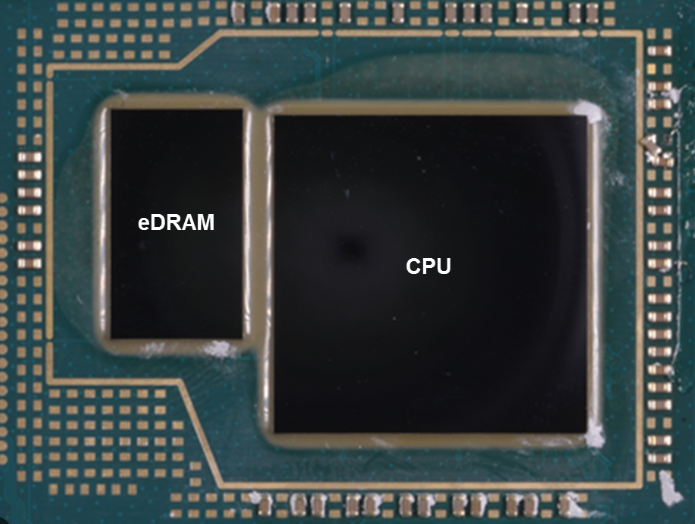

2T 0C의 Capacitor는 eDRAM(embeded - DRAM)의 형태로 CPU에 embeded 되어 동작을 할 수 있는 큰 이점이 있습니다. 삼성, TSMC, Intel과 같은 기업들이 해당 방식의 연구를 활발히 진행해오고 있죠. AMD와 같은 경우는 V-Cahse의 형태로 연구를 하고 있지만요.

그렇다면 Capacitor가 없는 이 2T0C 소자의 구조는 어떻게 되어있고, 어떤 방식으로 동작을 하는 것일까요?

eDRAM의 이름과 같이 SRAM의 역할을 대체 할 수 있는 대안으로 나온 소자입니다. BEOL의 공정에서 이어서 공정이 가 능하다는 매우 큰 장점이 있고 무엇보다 Capacitor가 없다는 것이 가장 큰 장점이죠. 그렇기 때문에 3D DRAM으로의 Stacking을 통한 확장 가능성도 있습니다.

2T 0C eDRAM에 사용되는 NEW Materials

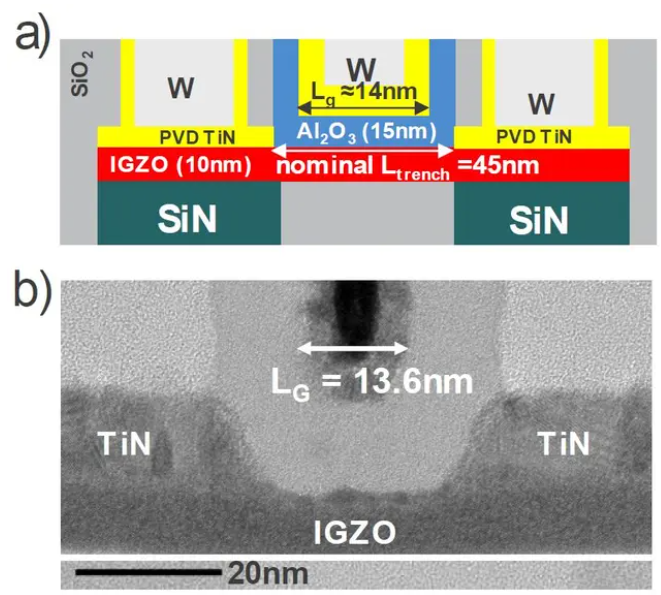

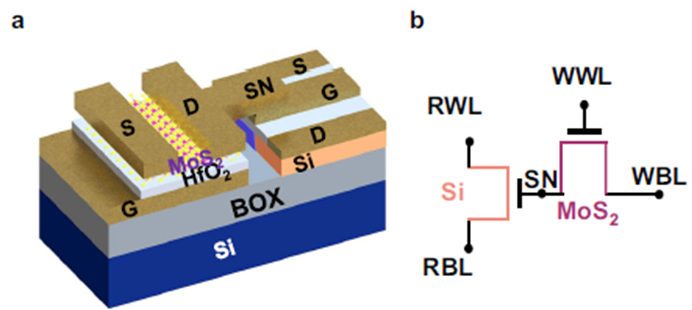

최근 가장 각광 받고 있는 물질은 IGZO가 아닐까 싶습니다. 그리고 Si과 MoS2를 동시에 사용한 heterostructure의 transistor가 주인공이 아닐까 싶네요.

IGZO를 활용한 소자의 경우에는 기생 Capacitance를 활용하여 전하를 저장하는 소자입니다.

반면에, Si과 MoS2를 활용한 소자는 2D물질로 일컫는 MoS2의 큰 bandgap(~1.29eV)를 전하 Trap 물질로 활용하여 전하를 저장합니다. 그래서 MoS2를 활용한 Transistor는 Write 동작에 활용되고 Si은 Read 동작에 활용이 되는 Transistor입니다. Si을 활용하면 on current가 높은 장점 그리고 기존 Si 기반 공정과 활용가능성이 있기 때문에 또 강점을 가지고 있죠.

위의 사진이 IGZO를 활용한 소자입니다.

위 사진이 Si과 MoS2를 활용한 2T0C 소자입니다.

위 소자에 대해서 조금 더 설명을 덧붙이자면,

MoS2는 매우 낮은 off current를 가지고 있기 때문에 data retention 특성이 매우 우수합니다.

그래서 거의 반 영구적으로 data 저장을 할 수 있는 것이죠.

그리고 Si Transistor는 높은 On current로 S/A Margin 확보에 유리합니다. 또 앞서 언급드렸지만, Si을 활용하기 때문에 공정적인 이점도 분명히 있구요.

이렇듯, Si+MoS2 heterostructure eDRAM이 최근 떠오르고 있는 추세인 분위기입니다. 아직은 산업화에 긴 여정이 남았지만요.

여기까지 최근 DRAM의 몇가지 이슈들과 그 과정에서 등장한 2T0C 라는 새로운 Capacitorless 소자에 대해서 설명을 드렸습니다. 아직까지 정확한 동작 메카니즘과 전기적인 특성에 대해서는 관련 논문을 찾아보지 않았기 때문에 추후 관련 글을 작성하게 된다면 첨부할 수 있도록 하겠습니다.

'반도체 공부' 카테고리의 다른 글

| [반도체 공정] Photolithography 공정, 노광 공정 그리고 PhotoResist(PR)에 대하여 & EUV 장비는 무엇인가? (0) | 2024.11.23 |

|---|---|

| XPS(Xray Photoelectron Spectroscopy) 데이터 분석 방법, Data Calibration (4) | 2024.11.12 |

| [반도체 물성, 물리전자] 반도체 소자의 Scaling Down 그리고 무어의 법칙(Moore's Law) (0) | 2024.06.12 |

| [반도체 물성, 물리전자] 분극(Polarization)이란? 분극의 종류 - 전자분극, 이온분극, 배향분극 (0) | 2024.06.08 |

| [DRAM Capacitor] 종류와 동작원리 그리고 SDRAM,SDR, DDR (0) | 2024.06.06 |